關於 VPX 系統整合的 Elma 提示:什麼是 SYS_CON*、NVMRO 和可遮罩套組 *?

在 Elma,我們不僅會收到大量銷售前問題,我們還在設計階段、初步設計審查和重要設計審查期間提出了很多問題,更不用說標準和定制產品的所有售後問題。因此,當同樣的問題不斷出現時,我們知道這是很多客戶希望聽到的事情。

近 40 年來,我們一直為業界提供高品質的嵌入式計算產品,從擠出機和卡片導引到所有產品 背板, 底盤, 板,以及集成系統。我們的成功來自我們的客戶,以及他們的問題和反饋,這有助於我們做得更好的事情。

我們一直接收到的問題

在這個 Elma 提示中,我們將解決 VPX 系統整合的一些非常基本的起點。客戶經常問我們 SYS_CON*、NVMRO 和 MaskableReset* 是什麼用的,或者我們會收到無法使系統運作的人的支持電話,而事實證明這三個信號中的一個或多個背板上是問題。

SYS_CON*-您的系統控制器

這是交易:OpenVPX 系統需要有一個插槽,只有一個插槽,指定為系統控制器。

在 Elma 背板上,每個插槽都有一個 2 針頭接頭連接器,一個引腳上有 SYS_CON*,另一個接腳上有數字接地。您需要在這個 2 引腳接頭上安裝一個跳接器,以告訴該插槽中的主機板「嘿,您是系統控制器。」系統控制器會在背板上驅動過濾的 REF_CLK,以供其他主機板使用。

如果沒有插槽指定為系統控制器,則系統可能無法運作。看起來很簡單,但我們一直在與客戶服務,他們花了數小時的疑難排解,才發現他們忘記了這個重要步驟。

NVMRO-非揮發性記憶體唯讀 (AKA 寫入保護)

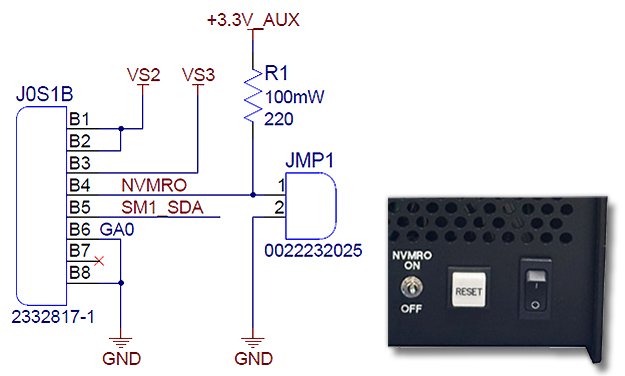

NVMRO 基本上就像寫入保護信號。我們的背板包括 3.3_AUX 的拉伸電阻器,如果您不用處理,NVMRO 會保持堅定(保護寫入)。

Elma 背板還具有一個 2 針頭接頭連接器,一個引腳上具有 NVMRO,另一個接腳上有數字接地。在這兩個接腳上安裝一個跳接器以解除 NVMRO 並允許寫入。在某些 系統,我們將這些引腳連接到交換器或機箱 I/O,因此您可以輕鬆地遠端控制 NVMRO。

這是我們收到的經典支持電話:有人嘗試更新主機板上的固件,經過多次嘗試後,他們無法更改固件。他們在拔出頭髮,想知道怎麼了事實證明,NVMRO 被確認,並且不會讓固件更新。我們告訴他們安裝跳接器以消除 NVMRO 的強度,並且擴展 — 韌體升級正常運作。

遮罩組 *-大多數人不使用的信號

除了全域 SYSRESET* 之外,除了全域 SYSRESET* 之外,還提供了一個外掛模組的可選本機重設輸入。老實說,我們很少看到客戶使用 MaskableReset* 信號。

但是,由於我們許多背板設計都在每個插槽上都包含一個 2 引腳接頭連接器,可讓您將該插槽的 MaskableReset* 信號連接到背板上的通用 MaskableReset* 信號。然後還有另一個 2 引腳接頭,其中一個引腳上具有通用的 MaskableReset* 信號,另一個接腳上有數字接地。

這就是它變得有趣的地方: 我們已經看到人們沒有特殊原因在這些標頭上安裝跳接器,結果是他們的插件卡被保持在重置狀態。卡片只是坐在那裡,什麼都沒事了。因此,以下是一些好的建議:除非您的話,否則不要安裝這些跳接器 其實 需要它們。

最底線

這三個信號似乎很簡單,但是誤解它們可能會導致嚴重頭痛:

• SYS_CON*:確定正確安裝了一個插槽的跳接器

• NVMRO:在嘗試韌體更新之前,請檢查寫入保護是否關閉

• 遮罩設定 *:除非您特別需要本地重置控制,否則將跳接器放在外

當客戶發生神秘的系統問題給我們打電話時,檢查這三個信號通常是我們的開始。正確使用這些功能,您將節省大量故障排除時間。

需要協助嗎?

有關這些信號或其他信號的問題 VPX 整合 挑戰?給我們打電話。我們可能已經看過您所處理的任何問題,我們在這裡幫助您解決問題。

FAQs

這些是 VPX/OpenVPX 系統整合中用於控制基本行為的公用程式背板信號:SYS_CON* 指定系統控制器,NVMRO 控制非揮發性記憶體寫入保護,而 MaskableReset* 為外掛模組提供選擇性的本地重設輸入。

SYS_CON* 告訴系統哪個插槽被指定為系統控制器-負責驅動參考時鐘(REF_CLK)和管理系統操作的主機板。只有一個插槽應通過跳接器確認 SYS_CON*

VPX 系統必須具有一個系統控制器才能正常運作。沒有它,模塊可能無法接收參考時鐘或初始化信號,並且系統可能無法運行

NVMRO 代表非揮發性記憶體唯讀,並充當寫入保護信號。默認情況下確認時,它會防止韌體寫入。若要更新韌體,必須解除 NVMRO(通常是安裝跳線器),以便允許寫入。

在許多背板上,連接到 NVMRO 的 2 引腳接頭可以跳接到地面以消除固定寫入保護,進而允許韌體更新。某些系統將此接頭連接到用於遙控的開關。