Elma-TIPPS für die VPX-Systemintegration: Was zur Hölle sind SYS_CON*, NVMRO und MaskableReset*?

Bei Elma erhalten wir nicht nur jede Menge Fragen vor dem Verkauf, wir beantworten auch viele Fragen während der Designphasen, vorläufigen Designprüfungen und kritischen Designprüfungen, ganz zu schweigen von allen Fragen nach dem Verkauf sowohl für Standard- als auch für kundenspezifische Produkte. Wenn also immer wieder dieselbe Frage auftaucht, wissen wir, dass viele Kunden davon hören möchten.

Seit fast 40 Jahren beliefern wir die Industrie mit hochwertigen Embedded-Computing-Produkten — von Extrusionen über Kartenführungen bis hin zu Backplanes, Fahrgestell, Bretterund integrierte Systeme. Unser Erfolg beruht auf unseren Kunden und ihren Fragen und Rückmeldungen, die uns helfen, die Dinge besser zu machen.

Die Fragen, die uns immer wieder gestellt werden

In diesem Elma-TIPP werden wir uns mit einigen sehr grundlegenden Ausgangspunkten für die VPX-Systemintegration befassen. Kunden fragen uns oft, wofür SYS_CON*, NVMRO und MaskableReset* gedacht sind, oder wir erhalten Support-Anrufe von Leuten, die ihre Systeme nicht zum Laufen bringen können, und es stellt sich heraus, dass es sich um ein Problem mit einem oder mehreren dieser drei Signale auf der Backplane handelt.

SYS_CON* - Ihr Systemcontroller

Hier ist der Deal: Ein OpenVPX-System muss einen Steckplatz und nur einen Steckplatz haben, der als Systemcontroller bezeichnet wird.

Auf Elma-Backplanes hat jeder Steckplatz einen 2-poligen Header-Anschluss mit SYS_CON* auf einem Pin und einer digitalen Masse auf dem anderen. Sie müssen an dieser 2-poligen Steckleiste einen Jumper für einen Steckplatz anbringen, um der Platine in diesem Steckplatz mitzuteilen: „Hey, Sie sind der Systemcontroller.“ Der Systemcontroller steuert den REF_CLK-Bus über die Rückwandplatine, damit andere Platinen ihn verwenden können.

Wenn kein Steckplatz als Systemcontroller vorgesehen ist, funktioniert Ihr System wahrscheinlich nicht. Scheint einfach genug, aber wir haben schon mit Kunden zusammengearbeitet, die Stunden damit verbracht haben, Probleme zu beheben, nur um dann festzustellen, dass sie diesen wichtigen Schritt vergessen haben.

NVMRO — Nur lesbarer nichtflüchtiger Speicher (AKA Write-Protection)

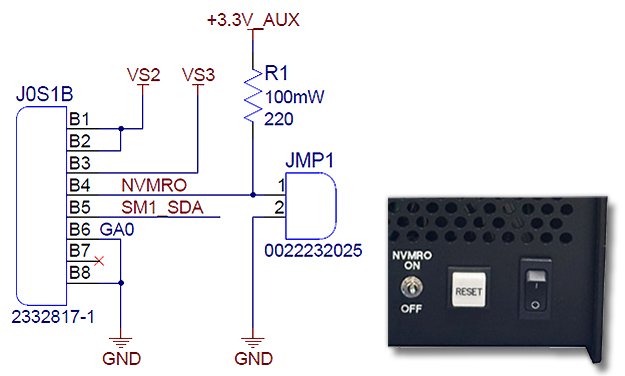

NVMRO ist im Grunde wie ein Schreibschutzsignal. Unsere Backplanes verfügen über einen Pull-Up-Widerstand gegen 3.3_AUX, und wenn Sie ihn in Ruhe lassen, bleibt NVMRO erhalten (schreibgeschützt).

Elma-Backplanes verfügen außerdem über einen 2-poligen Header-Anschluss mit NVMRO auf einem Pin und digitaler Masse auf dem anderen. Installieren Sie an diesen beiden Pins einen Jumper, um die NVMRO abzuschalten und Schreibvorgänge zu ermöglichen. In einigen Systeme, wir verbinden diese Pins mit einem Switch oder einem Gehäuse-I/O, sodass Sie NVMRO problemlos fernsteuern können.

Hier ist ein klassischer Support-Anruf, den wir erhalten: Jemand versucht, die Firmware auf einem Board zu aktualisieren, und nach zahlreichen Versuchen kann er die Firmware nicht ändern. Sie raufen sich die Haare und fragen sich, was los ist. Es stellte sich heraus, dass NVMRO behauptet wurde und die Firmware nicht aktualisieren ließ. Wir sagen ihnen, sie sollen den Jumper installieren, um die NVMRO abzuschalten, und Bumm — das Firmware-Upgrade funktioniert einwandfrei.

MaskableReset* - Das Signal, das die meisten Leute nicht verwenden

MaskableReset* ist ein optionaler lokaler Reset-Eingang für ein Plug-in-Modul, der zusätzlich zum globalen SYSRESET* bereitgestellt wird. Ehrlich gesagt sehen wir selten, dass Kunden das MaskableReset*-Signal verwenden.

Da viele unserer Backplane-Designs jedoch an jedem Steckplatz einen 2-poligen Header-Anschluss enthalten, können Sie das MaskableReset*-Signal dieses Steckplatzes mit einem gemeinsamen MaskableReset*-Signal auf der Backplane verbinden. Dann gibt es noch einen weiteren 2-poligen Header, der auf einem Pin das gemeinsame MaskableReset*-Signal und auf dem anderen eine digitale Masse hat.

Hier wird es interessant: Wir haben Fälle gesehen, in denen Leute ohne besonderen Grund Jumper an diesen Headern installiert haben und das Ergebnis war, dass ihre Steckkarten zurückgesetzt wurden. Die Karten lagen einfach da und haben nichts getan. Also, hier ein paar gute Ratschläge: Installieren Sie diese Jumper nur, wenn Sie tatsächlich brauche sie.

Die Quintessenz

Diese drei Signale mögen einfach erscheinen, aber wenn sie falsch verstanden werden, kann das zu großen Kopfschmerzen führen:

• SYS_CON*: Stellen Sie sicher, dass der Jumper genau in einem Steckplatz installiert ist

• NVMRO: Vergewissern Sie sich, dass der Schreibschutz ausgeschaltet ist, bevor Sie Firmware-Updates versuchen

• MaskableReset*: Lassen Sie die Jumper weg, es sei denn, Sie benötigen ausdrücklich eine lokale Reset-Steuerung

Wenn Kunden uns wegen rätselhafter Systemprobleme anrufen, beginnen wir oft mit der Überprüfung dieser drei Signale. Wenn Sie diese richtig machen, sparen Sie sich viel Zeit bei der Fehlerbehebung.

Brauchen Sie Hilfe?

Habe Fragen zu diesen oder anderen Signalen? VPX-Integration Herausforderungen? Rufen Sie uns an. Wir haben wahrscheinlich schon einmal das Problem gesehen, mit dem Sie sich befassen, und wir sind hier, um Ihnen zu helfen, es zu lösen.

FAQs

Dies sind Utility-Backplane-Signale, die bei der VPX/OpenVPX-Systemintegration zur Steuerung wesentlicher Verhaltensweisen verwendet werden: SYS_CON* bezeichnet den Systemcontroller, NVMRO steuert den Schreibschutz für nichtflüchtigen Speicher und MaskableReset* bietet einen optionalen lokalen Reset-Eingang für Plug-in-Module.

SYS_CON* teilt dem System mit, welcher Steckplatz als Systemcontroller bestimmt ist — die Platine, die für die Steuerung der Referenzuhr (REF_CLK) und die Verwaltung des Systembetriebs verantwortlich ist. Nur bei einem Steckplatz sollte SYS_CON* über einen Jumper bestätigt werden

Ein VPX-System muss genau einen Systemcontroller haben, um ordnungsgemäß zu funktionieren. Ohne sie empfangen die Module möglicherweise nicht die Referenzuhr oder die Initialisierungssignale, und das System funktioniert wahrscheinlich nicht

NVMRO steht für Non-Volatile Memory Read-Only und wirkt wie ein Schreibschutzsignal. Wenn es standardmäßig aktiviert ist, verhindert es Firmware-Schreibvorgänge. Um die Firmware zu aktualisieren, muss NVMRO deaktiviert werden (häufig durch Installation eines Jumpers), damit Schreibvorgänge zulässig sind.

Auf vielen Backplanes kann ein 2-poliger Header, der mit dem NVMRO verbunden ist, an die Masse angeschlossen werden, um den Schreibschutz zu deaktivieren und Firmware-Updates zu ermöglichen. Einige Systeme verbinden diesen Header zur Fernsteuerung mit einem Switch.