## Systems By Design

## 8100 – 64b/66MHz Metering PMC to PMC extender

# The Metering PMC to PMC extender is a comprehensive development tool for use with PMC cards on a VMEbus, Compact PCI, or other carrier card.

The primary function is to connect the carrier card PMC JN1, JN2, JN3, and JN4 connectors to a second set of connectors onto which a PMC under test is plugged in. This second set of connectors is positioned at the end of the extender card such that user's have the majority of the SIDE 1 area of the PMC exposed for probing.

The extender supports 3.3V and 5V PCI bus signaling. The product will work with 33 MHz and 66 MHz clock speeds, and with either 32-bit or 64-bit bus widths. The user is cautioned that the round-trip insertion delay imposed by the signal propagation delay from one end of the extender to the other is approximately 2.1ns; this represents 15% of a 66 MHz clock cycle which must be accommodated by the system's bus cycle timing margins.

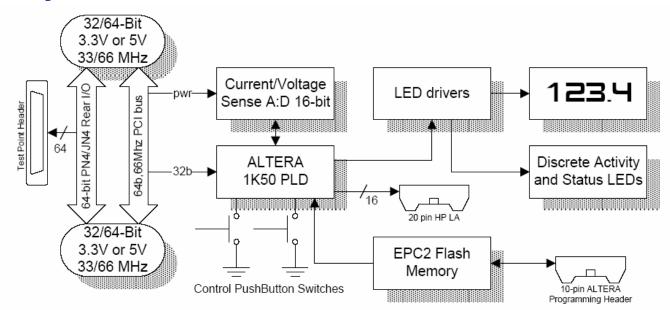

The board features self-resetting fuse protected power on +5V, +3.3V, +12V, and -12V supplies. Current sensing for these supplies is provided. The sensing networks use a series resistance (0.01 ohms) together with a differential amplifier to provide a voltage proportional to current. The voltage is digitized using a 16-bit A:D converter and the value is converted into a 4-digit LED display using an ALTERA PLD.

Current and Voltage of the supplies may be selected for display. Also, the ALTERA PLD can be set up to display bus bandwidth in Megabytes/sec for either the aggregate bus bandwidth or the bandwidth consumed by the PMC under test. Push-button switches on the extender select these functions. The metering functions include Min, Max, Max-Min, real-time display at averaging intervals of 256, 4096, 64K, and 1Meg samples from the 16-bit A:D converter. The meter design provides on-the-fly auto-zeroing and calibration parameters stored in an on-board EEPROM.

Discrete LEDs provide display of PCI bus activity (pulse stretched by the ALTERA PLD design), power supply tolerance within +/-5%, and selected metering modes.

The ALTERA PLD program is automatically loaded from an EPC2 FLASH memory chip on the board. This is pre-programmed with all the code necessary to support the LED and metering functions. The ALTERA design is available for those users who are capable and interested in implementing their own functions. Only the 32-bit PCI bus is connected to the ALTERA PLD.

A 20-pin header compatible with HP logic analyzer termination adapters is connected to the ALTERA PLD. This provides 16 Logic Analyzer channels worth of observation. The supplied PLD program provides synchronously buffered PCI bus control lines (FRAME, IRDY, TRDY, etc) on these signals, which may be modified by changing the ALTERA design. For a complete logic analysis solution for the PCI bus, consider the ACTTechnico 8095 analysis probe.

Individual signal probing of the 64 "user I/O" (JN4/PN4) at a 0.1" centered header along the bottom edge of the board.

This extender has been designed to support Processor PMC use and provides monitoring of the monarch, RSTOUT, GTNB, REQB and EREADY signals.

#### **BlockDiagram**

### **Technical Data**

#### Power

+5 Volt, 3.3V or 5V PCI signaling environment

**Environmental Operating Storage/Transit** Temperature:  $+5^{\circ}$  C to  $+50^{\circ}$  C Humidity (NC): 5% to 90% @  $40^{\circ}$  C

#### ElectromagneticCompatibility(EMC)

Intended for use in systems meeting the following regulations: U.S.: FCC Part 15, Subpart B, Class A (non-residential)

Canada: ICES-003, Class A (non-residential)

ACT/Technico, a division of Advanced Control Technology, Inc.

One Ivybrook Blvd., Suite 180, Ivyland, PA 18974 Tel (215) 957-9102 Fax (215) 957-9074

Form # 8100 - Rev. 06/04